## **Agilent ParBERT 81250 Parallel Bit Error Ratio Tester**

Product Overview Version 5.1 (Corresponds to ParBERT 81250 Software revision 5.1)

The Only Parallel Bit Error Ratio Solution for testing at 675 Mbit/s, 1.65 Gbit/s, 2.7 Gbit/s, 3.35 Gbit/s, 10.8 Gbit/s, 13.5 Gbit/s and 45 Gbit/s

## Agilent ParBERT 81250

Agilent ParBERT 81250 is a modular parallel electrical and optical bit error ratio (BER) test platform, which works up to 45 Gbit/s. The ParBERT 81250 platform comprises modules that work at 675 Mbit/s, 1.65 Gbit/s, 2.7 Gbit/s, 3.35 Gbit/s, 10.8 Gbit/s and 45 Gbit/s. The system generates pseudo random word sequences (PRWS), standard pseudo random binary sequences (PRBS) and userdefined patterns on parallel lines. You can analyze bit error ratios with userdefined patterns. PRBS/PRWS or mixed data (a combination of userdefined patterns and PRBS).

ParBERT 81250 is a perfect fit for parallel-to-serial, serial-toparallel, serial-to-serial and multiple serial BER test. Examples comprise multiplexer and demultiplexer (Mux/Demux) - or SerDes (serializer/deseralizer) testing used in telecom and storage area network (SAN) ICs, multiple transmitter and receiver testing in manufacturing, amplifiers as well as 10GbE and forward error correction (FEC) device testing. ParBERT 81250 also provides data and control signals for the DUT if required.

#### The ParBERT Software Suite is a ready-to-use package, which offers different levels of measurement analysis:

1. Fast pass/fail measurements ideal for production 2. Output Timing measurements provide results for setup & hold times, skew between channels, phase margins, detailed Jitter results (RJ/DJ/TJ), and eye opening specification results 3. Output level measurements provide results for high/low levels, amplitudes, threshold margins and Q-factor analysis **4.** Graphical results for detailed root cause analysis - see trends clearly and fast, e.g. color and contour plots

# Agilent ParBERT 81250 is particularly suitable for the following applications:

**1.** 10GbE device testing

- 2. Multiplexer and Demultiplexer Test

- OC-768 device testing: You can test 16:1 and 4:1 40G devices using the ParBERT 81250 45G and either 3.3 Gbit/s or 10.8 Gbit/s modules

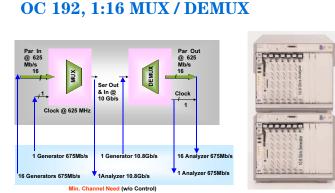

- OC-192 device testing: The ParBERT 81250 10.8 Gbit/s modules enable testing of the serial high-speed side of Muxes/DeMuxes. Combined with 675Mbit/s, 1.6Gbit/s, 2.7Gbit/s or 3.3 Gbit/s modules you can test both sides of multiplexers/demultiplexers

- OC-48 device testing

- **3.** Characterization of SAN ICs

- 4. Manufacturing Test of multiple Transmitters, Receivers, Transceivers and Amplifiers

- 5. FEC Device Test

For more information on these applications, please see brochure p/n 5968-9250E. For information on the Agilent ParBERT 81250 45 Gbit/s, please see p/n 5988-3020EN. For more information on ParBERT 3.35 Gbit/s optical/electrical mod-ules, please see p/n 5988-5901EN. This document focuses on the ParBERT platform up to 10.8 Gbit/s.

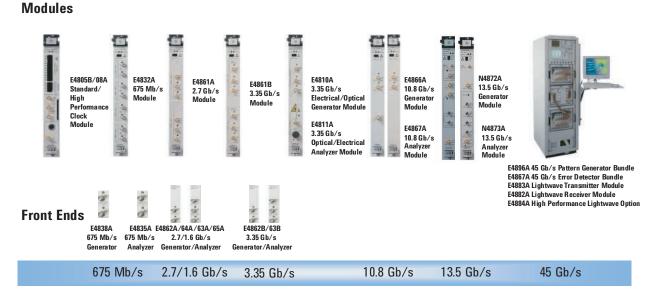

Figure 1: ParBERT Product Family

## ParBERT 81250 Key Features & Benefits

| Features                                                                                                                                                                                    | Benefits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modular, flexible and scalable platform architecture<br>· Up to 128 channels @ 675 Mbit/s<br>· Up to 64 channels @ 3.35 Gbit/s, 2.7 Gbit/s<br>· Up to 30 channels @13.5 Gbit/s, 10.8 Gbit/s | <ul> <li>Grows with customer's test and application needs</li> <li>Covers a wide range of technologies and applications</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Generator and Analyzer modules available from 675 Mbit/s up to 45 Gbit/s                                                                                                                    | Allows the configuration of a system to fit the customer's application needs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Mix of channels (generator/analyzer) and speed classes                                                                                                                                      | Provides unique flexibility to test complex devices with many channels and/or frequencies, e.g. Serial bus applications, Mux/Demux (SerDes), FEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Generate pseudo random word sequences (PRWS) and standard PRBS up to 2 <sup>31</sup> -1; Analyze bit error ratios with user-defined data, PRBS or mixed data from parallel ports            | Perform parallel BER measurements - ideal for Mux/Demux applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Generate and analyze single-ended, low voltage and differential signals - including true differential                                                                                       | <ul> <li>Test logic technologies e.g. LVDS, ECL, PECL, SSTL-2</li> <li>Generate the necessary signals to perform margin tests,<br/>emulate frequency and level changes and stress your device as<br/>far as possible</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                             |

| Data generation and analysis with sequencing and looping                                                                                                                                    | <ul> <li>Generate complex sequences that contain memory-based (up to 32Mbit) and/or PRBS/PRWS data</li> <li>Generate data packets with header and payload</li> <li>React to control signals from the DUT</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| Auto phase & auto delay alignment                                                                                                                                                           | <ul> <li>Auto alignment of expected data with incoming data</li> <li>Save time as you do not need to find the correct sample point<br/>manually - typically takes just 100ms, so ideal for<br/>manufacturing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |

| Each generator or analyzer channel has independent programmable control of voltage levels and timing delay                                                                                  | Allows device characterization for a wide range of technolo-<br>gies/applications in the semiconductor and communication<br>industry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Interrupt-free change of analyzer delay/generator<br>delay (13.5 Gbit/s and 3.35 Gbit/s; other speed classes<br>generator only)                                                             | Continuous running signals for measurements where changing analyzer delay is necessary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Jitter modulation (13.5 Gbit/s and 3.35 Gbit/s)                                                                                                                                             | Allows jitter tolerance testing to be performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Variable Cross (13.5 Gbit/s and 3.35 Gbit/s)                                                                                                                                                | Provides real-world stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Windows <sup>®</sup> 2000/NT 4.0 based user software                                                                                                                                        | Provide "standard" and "detailed" views for performing<br>measurements fast and efficiently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Plug and play drivers                                                                                                                                                                       | Allows remote access and simplifies remote program<br>development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Measurements Suite                                                                                                                                                                          | <ul> <li>DUT output timing measurement - bathtub curve with jitter<br/>analysis (RJ/DJ separation), skew between channels, setup<br/>and hold times</li> <li>Output level measurement - amplitude information, high/low<br/>level and Q-factor</li> <li>Eye opening measurement - color and contour plots</li> <li>Fast eye mask measurement - automatic threshold adjust, fast<br/>and efficient insights for manufacturing test</li> <li>Comprehensive BER measurement - actual and accumulated<br/>BER, errors of ones and zeros, total bits transferred and file<br/>capturing for post-processing analysis.</li> </ul> |

## Key Features (continued)

## Perform Parallel BER measurements up to 13.5 Gbit/s

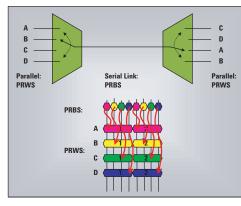

ParBERT 81250 makes testing of Mux/Demux (serializer/ deserializer) devices easier. Only ParBERT 81250 is able to generate pseudo-random-word sequences (PRWS) on the parallel side and analyze bit-error-ratios with user-defined patterns, PRBS up to 2<sup>31</sup>-1 or both combined.

# PRBS/PRWS and memory capability

The polynomial  $2^{n-1}$ , the PRBS algorithm and the parallel bus width define PRWS. The bits of the PRWS are assigned to parallel lines and are then multiplexed to form a PRBS (see figure 3).

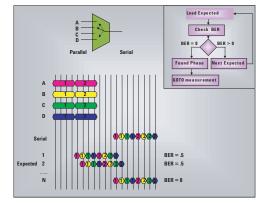

### Auto phase and auto delay alignment

As the latency from the input to the output is often not known exactly, or it is not deterministic, synchronization between incoming data and outcoming data has to be carried out. ParBERT 81250 has three capabilities to synchronize/align the incoming data automatically (see figures 4 and 5):

1) Data shift bit-by-bit if PRBS is used

2) Detect Word if user-defined patterns are used

3) Moving of the sampling point delay of the analyzer up to 10ns without stopping the instrument. Moving of the sampling point delay can also be used in addition to the alignment of data patterns (1 and 2) to refine the synchronization.

| 🛃 Eile    | III Edet Measurement Control System Window Help                                 |            |               |                    |                       |                     |                               |                             |                 |                 |                       |                           |

|-----------|---------------------------------------------------------------------------------|------------|---------------|--------------------|-----------------------|---------------------|-------------------------------|-----------------------------|-----------------|-----------------|-----------------------|---------------------------|

| ] 🗅 🖻     |                                                                                 |            |               |                    |                       |                     |                               |                             |                 |                 |                       |                           |

| Start: 07 | Start: 07/02/01 16:13:18 Stop: 07/02/01 16:13:36 Single Mode Elapsed Time: 15.5 |            |               |                    |                       |                     |                               |                             |                 |                 |                       |                           |

| Port/Term | ninal                                                                           |            | Actual<br>BER | Actual<br>Compared | Actual # of<br>Errors | Accumulative<br>BER | Accumulative<br>Compared Bits | Accumulative # of<br>Errors | Actual<br>0 BER | Actual<br>1 BER | Actual#of<br>0 Errors | Actual # of /<br>1 Errors |

| 🖃 🔯 Me:   | asurement                                                                       |            | 8             |                    |                       | 8                   |                               |                             |                 |                 |                       |                           |

| 0         | [2] Data                                                                        | <u>**</u>  | 🛿 2.500E-001  | 1.040E+000         | 2.600E (008           | 🛛 🔀 1.244E-CO1      | 1.474E+010                    | 1.834E+000                  | 2.500E-001      | 2.500E-001      | 0.00CE+000            | 2.600E 008                |

|           | 🔀 [2:1] Data1                                                                   | <u>۲</u>   | 🔀 5.000E-001  | 5.200E+008         | 2.630E+008            | 2.502E-C01          | 7.329E+009                    | 1.834E+009                  | 5.000E-001      | 5.000E-001      | 0.00CE+000            | 2.600E+008                |

| L_[       | [2.2] Cala0                                                                     | 1          | 0.000E+000    | 5.200E+008         | 0.000E+000            | 0.000E+C00          | 7.409E+009                    | 0.000E+000                  | 0.000E+000      | 0.000E+000      | 0.00CE+000            | 0.CO0E+000                |

| 自[3][     | Data                                                                            | <u>*</u> * | 0.000E+000    | 2.080E+009         | 0.000E+000            | 0.000E+C00          | 2.908E+010                    | 0.000E+000                  | 0.000E+000      | 0.000E+000      | 0.00CE+000            | 0.000E+000                |

| -1        | [3:1] Data3                                                                     | 🔧          | U.UUUE+UUU    | 5.300E+008         | U.UJUE+UUU            | U.UUUE+LUU          | 7.499E+009                    | U.UUUE+UUU                  | U.UUUE+UUU      | 0.000E+000      | U.UULE+UUU            | U.LUUE+UUU                |

| -[        | [3:2] Data2                                                                     | <u>م</u>   | 0.000E+000    | 5.300E+008         | 0.000E+000            | 0.000E+C00          | 7.199E+009                    | 0.000E+000                  | 0.000E+000      | 0.000E+000      | 0.00CE+000            | 0.000E+000                |

| -1        | [3:3] Data0                                                                     |            | 0.000E+000    | 5.100E+008         | 0.000E+000            | 0.000E+C00          | 7.039E+009                    | 0.000E+000                  | 0.000E+000      | 0.000E+000      | 0.00CE+000            | 0.000E+000                |

| L [       | [0:4] Data1                                                                     | <u>6</u> 2 | 0.000E+000    | 5.100E+000         | 0.000E+000            | 0.000E+C00          | 7.009E+009                    | 0.000E+000                  | 0.000E+000      | 0.000E+000      | 0.000E+000            | 0.000±4000                |

Figure 3: MUX/DEMUX Application: Relationship between PRBS and PRWS

Figure 4: Mechanism of auto-phase and auto-delay assignment

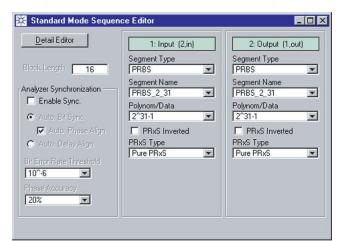

Figure 5: Standard view when choosing PRBS/PRWS patterns and data synchronization mode

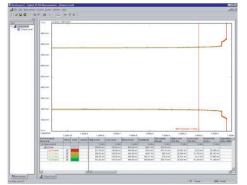

# Interrupt-free change of analyzer delay

The analyzer delay can be changed ±1 period whilst the instrument is running without causing it to stop see figure 6. The 13.5 Gbit/s and 3.35 Gbit/s modules can do this on the Analyzer and Generator.

| 🔆 Parameter Edit          |                          | _ ×   |  |  |  |  |  |  |

|---------------------------|--------------------------|-------|--|--|--|--|--|--|

| Resource: Output D        | ata Output Port)         | · + + |  |  |  |  |  |  |

| Timing Input              |                          |       |  |  |  |  |  |  |

| Data                      | Port                     |       |  |  |  |  |  |  |

| Actual Delay              | 1.25                     | ns    |  |  |  |  |  |  |

|                           | + N periods              |       |  |  |  |  |  |  |

| Start Delay (S            | System Restarts On Chang | je)   |  |  |  |  |  |  |

| Periods + Time            | 1.25                     | ns    |  |  |  |  |  |  |

|                           | 0.5                      |       |  |  |  |  |  |  |

| Periods                   |                          |       |  |  |  |  |  |  |

| Time                      | 0 🛨                      | ns    |  |  |  |  |  |  |

| Delay (No Stop On Change) |                          |       |  |  |  |  |  |  |

| 0                         | 0 Period                 |       |  |  |  |  |  |  |

| -1                        |                          | +1    |  |  |  |  |  |  |

|                           |                          |       |  |  |  |  |  |  |

Figure 6: Parameter Editor for analyzer timing

## **Multiple frequencies**

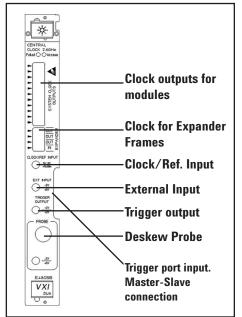

The modular architecture of ParBERT allows the use of different channels at different speeds. Therefore it is possible to combine channels of different speed classes in one ParBERT system. A ParBERT system can be configured with one or more clock groups. Each clock group is controlled from one clock module. Within one clock group (one clock module controls a group of channels) a frequency

ratio of  $2^{n}$ , n =1,2,....10 is possible, see figure 7.

| 🔆 Parameter Editor             |                                      |                        |                      |                   | _ ×             |  |  |  |  |

|--------------------------------|--------------------------------------|------------------------|----------------------|-------------------|-----------------|--|--|--|--|

|                                | Resource: C1 M1 Clk ("E4805B" F1 S0) |                        |                      |                   |                 |  |  |  |  |

|                                |                                      |                        |                      |                   |                 |  |  |  |  |

| Frequency Clock/Ref Input Exte | ernal Input                          | Trigger Oul            | put                  |                   |                 |  |  |  |  |

| Period 6.41025641026           | ns                                   | Delay Offset           | 0                    |                   | .▲<br>▼ ns      |  |  |  |  |

| Frequency 156                  | MHz                                  | Segment Re:            | solution 4           |                   | ✓ Bit           |  |  |  |  |

| Use Single Frequency           | ,                                    | Trigger<br>Frequency M | ultiplier 1          |                   | •               |  |  |  |  |

| Show All (Ports, Connectors)   | Frequency<br>Multiplier              | Actual<br>Frequency    | Maximal<br>Frequency | Segm.<br>Resolut. | Memory<br>Depth |  |  |  |  |

| 1: Data                        | 16 🔸                                 | 2.50 GHz               | 2.67 GHz             | 64 Bit            | 8 MBit 🔺        |  |  |  |  |

| 2: Data                        | 1 🔸                                  | 156.00 MHz             | 166.67 MHz           | 4 Bit             | 512 KBit        |  |  |  |  |

| C1 M3 C1                       | 4 🖊                                  | 624.00 MHz             | 666.67 MHz           | 16 Bit            | 2 MBit          |  |  |  |  |

| C1 M3 C2                       | 4 🔸                                  | 624.00 MHz             | 666.67 MHz           | 16 Bit            | 2 MBit          |  |  |  |  |

| C1 M5 C1                       | 1 📕                                  | 156.00 MHz             | 166.67 MHz           | 4 Bit             | 512 KBit        |  |  |  |  |

| C1 M5 C2                       | 1 🕴                                  | 156.00 MHz             | 166.67 MHz           | 4 Bit             | 512 KBit 🚽      |  |  |  |  |

| C1 M5 C3                       | 1 🖡                                  | 156.00 MHz             | 166.67 MHz           | 4 Bit             | 512 KBit 🗾      |  |  |  |  |

Figure 7: Parameter Editor for setting multiple frequencies in one system

With the two clock groups any frequency ratio m/n, n=1,2,...,256 is possible. The 'application examples' show some 'two-clocksystem' configurations

## Fundamental Platform Description

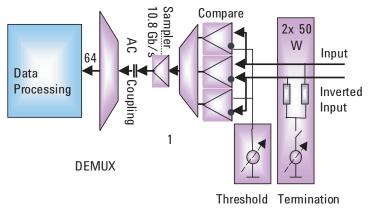

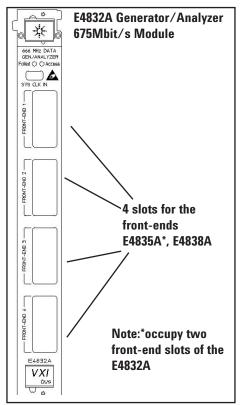

The idea of the ParBERT 81250 product structure is that you receive the instrument, which meets your measurement needs exactly. The ParBERT modularity offers modules and frontends. At 13.5 Gbit/s and 10.8 Gbit/s there are dedicated modules for Generators and Analyzers. At 3.35 Gbit/s, 2.7 Gbit/s, 1.6 Gbit/s and 675 Mbit/s the modules carry 2/4 front-ends. The front-ends determine which kind of output or input connectors your specific instrument has. This means front-ends determine the speed and input/output capabilities of your instrument. A mix of frontends is possible within the modules. The front-ends are placed in data modules, which are responsible for sequencing, generating and analysing of data patterns including PRBS/PRWS. These modules, plus at least one **clock module**, which generates the common system frequency of the instrument, are installed in the mainframe.

The VXI frame offers 13 slots. Assuming the use of the FireWire interface and one Clock module in place, the mainframe can hold up to 10 channels at 13.5 Gbit/s, 11 channels at the data rate of 10.8 Gbit/s, 22 channels at 3.35 Gbit/s, 2.7 Gbit/s and 1.65 Gbit/s or 44 channels at 675 Mbit/s. If more channels are needed there is the possibility of adding up to two expander frames to reach the maximum number of channels within one clock group. Additional clock modules are needed to set up systems which work with different clock speeds that are not divisible or multipliable by the factors 2, 4, 8, 16 (if E4832A is used) and 2 and 4 (if E4861A is used). For example, for testing 1:7 or 1:10 Mux/Demux devices two clock modules are required. Please check the Application Examples within the next chapter.

The ParBERT **81250 Software Suite** runs on an external PC, or a laptop, which is connected to the system via an IEEE 1394 PC link to VXI. The operating system is MS Windows<sup>®</sup> NT 4.0 or Win 2000. The ParBERT 81250 Software Suite consists of:

- Graphical User Interface

- Measurement Suite

- Software Tools (10GbE Tool,

- SONET/SDH Frame Generator

- VXI Plug & Play Driver

At runtime the software consists of several processes, see new figure. The firmware server controls the hardware and is the link between the graphical user interface and the Hardware Modules. Also the Measurement Software or any custom remote program can communicate with the Firmware Server. The remote access is established either by using the Plug and Play drivers from Agilent Vee or from a C/C++/Visual Basic program or by a SCPI based language via GPIB. This allows the building of a customized VXI system including other standard VXI modules.

|                      | 675 Mbit/s            | 2.7 Gbit/s/3.35 Gbit/s  | 10.8 Gbit/s           | 13.5 Gbit/s           |

|----------------------|-----------------------|-------------------------|-----------------------|-----------------------|

| Data Rate Range      | 333.3 Kbit/s          | 333.4 Mbit/s 2.7 Gbit/s | 9.5 10.8 Gbit/s       | 500 Mbit/s 13.5       |

|                      | 675 Mbit/s            | 20.8 Mbit/s 3.35 Gbit/s |                       | Gbit/s                |

| Number of Channels   |                       |                         |                       |                       |

| within 1 Frame / + 2 |                       |                         |                       |                       |

| Expander Frames      |                       |                         |                       |                       |

| with ext. PC         | 44/132                | 22/66                   | 11/33                 | 10/30                 |

|                      |                       |                         |                       |                       |

| Inputs/Outputs       |                       | differential & single   | differential & single | differential & single |

|                      | differential & single | ended                   | ended                 | ended                 |

| Data Capability      | ended                 | PRBS/PRWS/              | PRBS/PRWS/            | PRBS/PRWS/            |

|                      | PRBS/PRWS/            | 8/16 Meg Memory         | 32 Meg Memory***      | 64 Mbit Memory        |

|                      | 2 Meg Memory          | о ,                     | с ,                   |                       |

| Generator Formats    | 0 /                   | 2.7G:DNRZ               | DNRZ, separate        | NRZ, DNRZ             |

|                      | DNRZ, RZ, R1          | 50% clock               | clock output**        |                       |

|                      |                       | DNRZ, R1, RZ            | ·                     |                       |

| Technology           |                       | CML, (P)ECL*,           | CML, ECL,LVDS,        | LVDS, CML, PECL,      |

| addressed            | TTL, (P)ECL, LVDS     | LVDS, SSTL-2            | SSTL-2                | ECL, low voltage      |

|                      |                       | •                       |                       | CMOS                  |

#### Table 6 gives an overview on key specifications of the different speed classes:

Notes: \* for PECL a BIAS Tee at Analyzer input is needed

\*\* separate clock output is single ended only

\*\*\* balanced pattern only

Table 6: Key Specifications of ParBERT channels

| 10G Ethernet Tool                                                                                                                             |                                              |              |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------|--------------------------------------|

| Connection Generation/Expected                                                                                                                | Post Processing                              |              |                                      |

| XAUI         No. of B           Frame         0           Lane 0         Lane 1         Lane           0         0         0                  | Idle + 0                                     | Total<br>= 0 | No. of Frames<br>Total<br>CRC Errors |

| T 10GBASE-R No. of B                                                                                                                          | its<br>Idle<br>+ 0                           | Total        | No. of Frames<br>Total<br>CRC Errors |

| 0.0000       Bit Error Rate         Mode       Image: Single Measurement         Image: Single Measurement       Image: Multiple Measurements | Stop Condition<br>Until Break<br>for N Times |              | Start<br>Break                       |

Figure 7b: 10GbE Processing Tool

| 🔆 Sonet/SDH Frame Ge                   | nerator                              |                       |

|----------------------------------------|--------------------------------------|-----------------------|

| <u>F</u> ile <u>V</u> iew <u>H</u> elp |                                      |                       |

|                                        |                                      |                       |

| Mode<br>© Normal<br>© CID              | Frame(s)<br>© Single<br>© Multiple 2 | Errors<br>None        |

| Format<br>SONET<br>SONET-C<br>SDH      | Rate<br>STS 768                      | Alarms<br>None        |

| Scrambler<br>© On                      | All Os                               | Mask Analyzer B Bytes |

|                                        | Segment width: 🛨 16                  | Exit                  |

| ⊙ Off                                  |                                      | File Save Menu        |

| C On<br>Ready                          |                                      |                       |

Figure 7c: SONET/SDH Editor

| 5 1 8                        | ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| TxDSC                        | TXDATA14 TXDATA12 TXDATA10 TXDATA8 TXDATA6 TXDATA4 TXDATA2 TXDATA0<br>TXDATA15 TXDATA13 TXDATA11 TXDATA9 TXDATA7 TXDATA5 TXDATA3 TXDATA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 0.00e+000                    | [0.00e+000         [0.00e+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SKEV  |

| 0.00e+000                    | 0.00e+000 [0.00e+000 [ | BER   |

| Server and Sy<br>Server Name | Stem Properties  Connect Available Systems  Available Systems  Available Systems  Connect Conn | olute |

| Port Number                  | 2203 DSRA_DFF V Data V Update Ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ait   |

Fig 7d: SFI5 post processing

# Analyzing the data & the DSC (17th) bit:

- Ensure that the 16 data channels are valid (valid PRBS 2<sup>7</sup>-1 or 2<sup>11</sup>-1) streams:

- Ensure that the 16 data channels are within skew specification.

- $\cdot$  Ensure that the DSC (17th) bit is valid:

- correct header

- match to the 16 data channels

## **Measurement Software**

The ParBERT measurement software includes the following measurements: 1. BER Measurement 2. Fast Eye Mask Measurement

- 3. DUT Output Timing Measurement

- 4. DUT Output Level Measurement

- 5. Eve opening

The ParBERT 81250 measurement software is a ready-to-use measurement user interface, which aids you with the verification and characterization of highspeed digital components and modules.

The measurement software offers three different levels of measurement analysis: 1. Fast pass/fail measurements ideal for production.

If you work in production you can test against limits, e.g. the BER is set at a given threshold. The fast pass/fail measurements allow you to test devices at up to ten times faster than with previous test methods - it typically takes less than one second!

Past clock out to data out (setup and hold times), skew and eye opening specification results

no need to calculate values

Graphical results for detailed root cause analysis - see trends clearly and fast, e.g. pseudo color plot and contour plots.

If you are in R&D you can characterize your device under test (DUT), find the limits and specifications of the DUT and results can be viewed graphically.

With its easy-to-use Windows® 2000 or NT 4.0 based GUI and graphical results, it simplifies test development and allows easy test execution. Data can be exported and the graphical and numerical results printed.

| Table 1: General |                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                  | workspace                                                                                                                           |

| Store/recall     | Single Measurements                                                                                                                 |

| Copy/paste       | Measurement data to compare between measurements                                                                                    |

| Print            |                                                                                                                                     |

| Export of        | Measurement data (ASCII)                                                                                                            |

| On line help     |                                                                                                                                     |

|                  | P&P Driver,                                                                                                                         |

| Remote interface | Ready to use active X components to integrate<br>complete measurements easily in VEE, Visual<br>C++, VB, Labview, Mathlab and Excel |

You can create test executive around the measurement software using Agilent Vee, National Instruments' LabVIEW®, Excel, Agilent TestExec, C/C++ and Microsoft® VisualBasic.

The Measurement Software is included in the standard software package which comes with each ParBERT 81250 system.

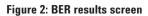

## **BER Measurement**

The Bit Error Ratio measurement measures the total number of bits transferred and the number of errored bits, bits which don't meet the decision threshold. You can now view the actual 0 and 1 BER, actual 0 and 1 errors, accumulative 0 and 1 BER and accumulative 1 and 0 errors at once. The Bit Error Rate measurement can be run as a single shot or repeatedly. Several run and error counting options and stop criteria can be defined. Repetitive mode offers automatic resynchronization. It is the ideal mode for characterizing your device, so good for R&D, for example, you can change the temperature and measure how it affects the BER. Single mode is particularly useful for manufacturing as you can stop the measurement after a specified number of errors and/or seconds.

Measurement results provided:

- Displayed errored ones and zeros at the same time

- · Log file

- · Resynchronization

- · Pass/fail results

| Measurement Parameters | BER                                |

|------------------------|------------------------------------|

|                        | Compared bits                      |

|                        | Errors from expected 0s            |

|                        | Errors from expected 1s            |

|                        | Total errors                       |

|                        | Parameters from last measurement   |

|                        | period                             |

|                        | Accumulated parameters             |

| Measurement mode       | Single or repetitive               |

|                        | Repetition rate is programmable in |

|                        | seconds (In this mode              |

|                        | resynchronization can be enabled)  |

| Pass/fail              | For actual and accumulated         |

|                        | parameters                         |

| Log file               | Logs all measured parameters       |

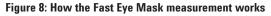

## **Fast Eye Mask**

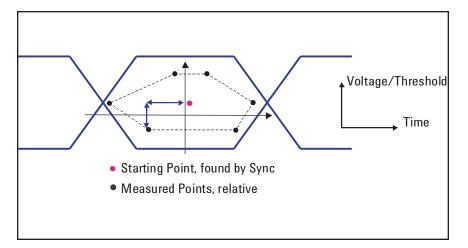

The fast eye mask measurement is ideal for use in manufacturing as a measurement typically takes just one second (including synchronization). This measurement records the BER of a pre-defined number of points (1 to 32), not the whole eye, defined by a threshold and timing value relative to the starting point of the measurement. You enter the pass/fail criteria of the measurement and the BER threshold, find the middle point of the eye with the sequence and then run the BER. For example, you can define a threshold and ParBERT will find the optimal sample point and the high and low levels automatically, e.g 20% and 80%.

Measurement results provided:

- $\cdot$  BER at pre-defined sample points

- $\cdot$  Pass/fail results

| fem_shp<br>rt/Terminal   | Copied | 1         | 2        | 3           | 4           | 5           | 6           | 7 | 8 | - 14 |

|--------------------------|--------|-----------|----------|-------------|-------------|-------------|-------------|---|---|------|

| Measurement              | Copied |           | 2        | 3           | +           | ,           | 0           |   | • | +    |

| - Relative Time          |        | -0.400 UI | 0.400 UI | -0.160 UI   | 0.160 UI    | -0.160 UI   | 0.160 UI    |   |   | +    |

| -Voltage(abs)            |        | 0.000 V   | 0.000 V  | 200.000 mV  | 200.000 mV  | -200.000 mV | -200.000 mV |   |   | +    |

| [1] ClockPort            |        | 0.000 1   | 0.000 1  | 200,000 111 | 200,000 111 | 200.000 111 | 200.000 111 |   |   | +    |

| 直[1:1] Cik0              |        | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | +    |

| [3] DataPort             |        |           |          |             |             |             |             |   |   | +    |

| 13:1] Data0              |        | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | +    |

| 13:2] Data1              |        | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | +    |

| 13:3] Data2              |        | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | 1    |

| 13:4] Data3              |        | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | +    |

| Copied 07/16/01 16:39:11 | Х      |           |          |             |             |             |             |   |   | +    |

| -Relative Time           | Х      | -0.400 UI | 0.400 UI | -0.160 UI   | 0.160 UI    | -0.160 U    | 0.160 UI    |   |   | 1    |

| -Vottage(abs)            | X      | 0.000 V   | 0.000 V  | 200.000 mV  | 200.000 mV  | -200.000 mV | -200.000 mV |   |   | +    |

| [1] ClockPort (Copied)   | Х      |           |          |             |             |             |             |   |   | +    |

| 田(1:1) Clk0 (Copied)     | х      | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | 1    |

| [] [3] DataPort (Copied) | Х      |           |          |             |             |             |             |   |   | 1    |

| 13:1] Data0 (Copied)     | Х      | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | 1    |

| 13:2] Data1 (Copied)     | Х      | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   |      |

| 13:3] Data2 (Copied)     | Х      | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   |      |

| 13:4] Data3 (Copied)     | Х      | 0.000     | 0.000    | 0.000       | 0.000       | 0.000       | 0.000       |   |   | 1    |

|                          |        |           |          |             |             |             |             |   |   |      |

Figure 9: The Fast Eye Mask set-up and results window

| Frequency | # channels | # points measured | Compared Bits   | Time Taken |

|-----------|------------|-------------------|-----------------|------------|

| 2.7Gbit/s | 2          | 6                 | 10 <sup>6</sup> | < 1 sec    |

| 2.7Gbit/s | 2          | 32                | 10 <sup>6</sup> | ~ 1 sec    |

| 675 MHz   | 16         | 6                 | 10 <sup>6</sup> | ~ 6 sec    |

| 675 MHz   | 16         | 32                | 10 <sup>6</sup> | ~ 6 sec    |

Table 3: Fast Eye Mask measurement time examples (run on a system via IEEE 1394 PC link)

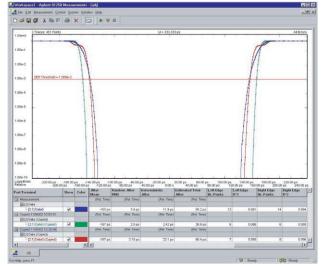

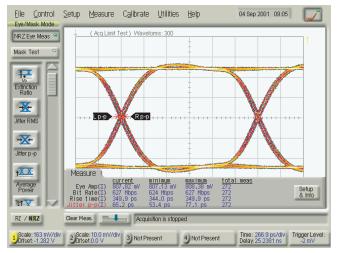

## **DUT Output Timing Measurement**

This measurement measures the BER of a DUT's output versus sample point delay, which is shown graphically as a bath tub curve. The delay is always centered to the optimum sampling delay point of the port (terminals). If a clock is defined the clock to data alignment is measured. If the absolute delay can be measured it will also be displayed. Relative timing, where edges are compared, is also possible.

Measurement results provided:

- · Clock out to data out timing relations (setup/hold time)

- $\cdot$  Skew between outputs

- $\cdot$  Delay at optimum sample point

- $\cdot$  Phase margin

- $\cdot$  Pass/fail results

- · Jitter results for total jitter, random jitter and deterministic jitter

There is also a numerical view that shows the "numerical return values" for the selected BER threshold only.

Figure 10a : View the DUT output measurement results as a bathtub curve

Figure 10b: Jitter can be directly equated from the bathtub curve. View the jitter as a histogram.

| Table 4: DUT Output Timing | Measurement                                |

|----------------------------|--------------------------------------------|

| Timing Parameters          | Optimum sample point delay                 |

|                            | Phase margin                               |

|                            | Clock to data out min                      |

|                            | Clock to data out max                      |

|                            | Skew between channels                      |

| Jitter Parameters          | RMS Jitter                                 |

|                            | Mean Value                                 |

|                            | Peak Peak Jitter for specific BER          |

| Pass /fail                 | For all timing and jitter parameters       |

|                            | Each parameter can be individually enabled |

| Graph                      | View of BER versus sample delay            |

|                            | 2 Markers: delay, BER                      |

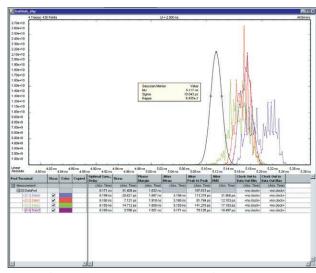

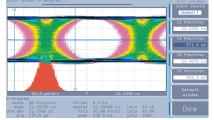

## **Output Level Measurement**

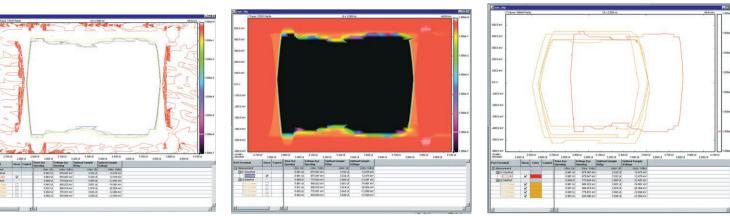

This measurement performs a sweep of the analyzer threshold. It is shown graphically as a bathtub curve, with the threshold on the Y-axis and BER on the X-axis (see figure 11a). From the data a histogram showing BER versus threshold can be derived (figure 11b) which can be used to calculate one/zero level means and standard deviations. Also a graph showing Q-factor from BER versus threshold (figure 11c) can be derived, which shows the result of two tail fitting operations for the innermost gaussian distributions in the BER histogram.

| Table 5a Output l | Level Measurement                                          |  |

|-------------------|------------------------------------------------------------|--|

| Measurement       | High/low level                                             |  |

| Parameters        | Mean level                                                 |  |

|                   | Amplitude                                                  |  |

|                   | Threshold margin                                           |  |

|                   | High/low level standard deviation                          |  |

|                   | Peak peak noise<br>Signal/noise ratio (rms & peak-to-peak) |  |

|                   |                                                            |  |

|                   | Q factor                                                   |  |

| Pass/fail         | For all parameters                                         |  |

|                   | Each parameter can be individually enabled                 |  |

| Graphs            | BER versus threshold                                       |  |

|                   | BER histogram versus threshold,                            |  |

|                   | Q from BER versus threshold                                |  |

Figure 11a) BER versus threshold

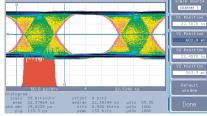

## Eye Opening

To measure the eye opening the sampling delay and the threshold of the receiving channels are swept.

Measurement results provided:

- Eye opening (voltage and timing)

- $\cdot$  Optimum sample point

11b) BER Histogram versus threshold

11c) Q from BER versus threshold

| <u>Table 5b: Eye opening</u><br>Meas.<br>Parameters | Optimum sample<br>point delay<br>Optimum threshold<br>Eye opening (Volt)<br>Phase margin |

|-----------------------------------------------------|------------------------------------------------------------------------------------------|

| Pass/fail                                           | For all parameters<br>Each parameter can be<br>Individually enabled                      |

Two markers:Voltage, Delay, BER

Graph

Figure 12 a/b/c: View the BER for one terminal as a pseudo color plot or contour plot or equal BER at BER Threshold

## **Application Examples**

#### **10GbE** 1x 81250A XSBI 16x644.53Mb PMD XAUI DUT 4 x 3.125G differential data (8B/10B encoded) (4:32 demux XAUI=>XGMII) 16:1 diff data TX 10B/8B dec 64B/66B enc, mux 10.3125G optical (66B/64B encoded diff clock +x<sup>39</sup>+1 scramler 32:16 mux, Clock 66B/64B dec, 1x E4866A diff clock x<sup>39+1</sup> descramler 1:16 RX 1x E4867A 8B/10B enc demux diff data w/ CDR 4 x 4:1mux 1 Analyzer 10.8Gb/s + O/E Converter 4 Analyzers 3.35Gb/s 4 Generators 3.35Gb/s 1 Generator 10.8Gb/s + E/O Converter

Figure 14a: 10GbE

Figure 15: OC 192 example

1x 81250A-149 1x E4875A 1x 81250A-013 4x E4808A 4x E4861B 4x E4862B 4x E4863B

1x 81250A

1x E4875A

2x E4808A

10x E4832A

17x E4838A

9x E4835A

1x E4866A

1x E4867A 1x 11667B

1x 81250A-149

1x 81250A-152

1x 81250A#013

#### **10GbE**

10GbE parts are used in the MAN area. The DUT is a module with 4x 3.125Gb/s electrical inputs and outputs each and 1x 10.3125Gbit/s optical input and output. The DUT supplies a clock of 156.25MHZ to all Systems. The optical signals are converted electrically.

The configuration of ParBERT 81250 for 10GbE testing includes four clock groups and E/O and O/E converters for the optical signals at 10.3125Gbit/s.

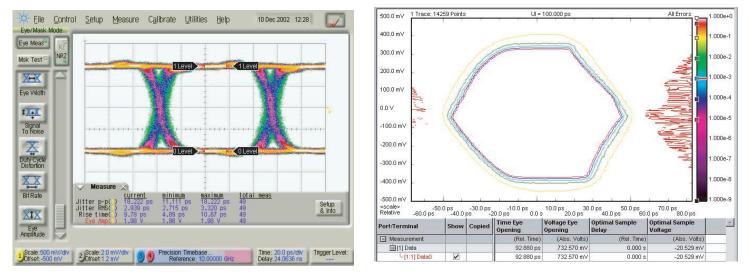

## **OC 192**

OC 192 parts are used in telecom applications. Here the DUT consists of two chips, one TX and one RX. There is no clock at the serial side. For testing 16x 675 Mbit/s Generators and Analyzers on the parallel side are needed. The serial side needs 1 times 13.5 Gbit/s or 10.8 Gbit/s Generator and Analyzer.

The 81250 configuration to the left contains all necessary resources to test Mux/Demux. Both parts of DUT can be tested at one run-time. regardless of whether memory-based data or PRBS/PRWS are used.

The 13.5 Gbit/s or 10.8 Gbit/s channels can be used together with the 675 Mbit/s channels, as the multiplier is 16 (another multiplier would require separation into 2 clock groups, similar to the other two examples). The combination of all generators and analyzers in individual clock groups eliminates the synchronization limitations.

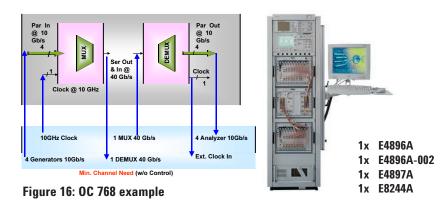

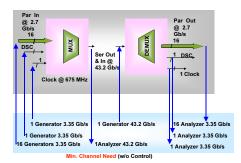

## **OC 768, 1:4 MUX / DEMUX**

## OC 768, 1;4 Mux/DeMux ratio

DUT consists of two chips, one TX one RX. There is no clock at the serial side. This will require 4x 10.8 Gbit/s Generator and Analyzer channels for the parallel side and 1x 43.2 Gbit/s Generator and Error Detector Bundle E4894A and E4895A.

The 81250 configuration, shown in Figure 16, contains all necessary resources to test Mux/Demux. Both parts of the DUT could be tested at one run-time using PRBS/PRWS data

## OC 768, SFI5 (1:17) MUX and DEMUX with ParBERT 3.35G modules @ parallel

Figure 16a: OC 768 SFI-5 Mux and DeMux

| 1x  | 81250A     |

|-----|------------|

| 1x  | 81250A-149 |

| 1x  | E4875A     |

| 1x  | 81250A-013 |

| 2x  | 81250A-152 |

| 2x  | E4808A     |

| 18x | E4861B     |

| 18x | E4862B     |

| 18x | E4863B     |

| 1x  | E4868A     |

| 1x  | E4869A     |

| 1x  | E8244A     |

|     |            |

### OC 768, SFI-5 (1:17) Mux/DeMux

The DUT consists of two parts: a TX and RX part. Characteristic for SFI-5 is the 17th bit, called DSC signal. This carries specific timing alignment data. The modular ParBERT 81250 architecture allows the easy addition of a 17th generator and analyzer channel to handle the DSC signal.

The 81250 configuration, shown in Figure 16a, contains all necessary resources to test SFI-5 Mux and Demux. Both parts of DUT can be tested but not at one run-time. The parallel side (3.35 Gbit/s) includes 18 generators and 18 analyzers, so beside the 16 data bits, the test system can handle the DSC signal (17th bit) and any clock if necessary.

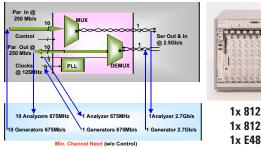

## Gigabit Ethernet, 1:10 MUX / DEMUX

**Figure 14: Gigabit Ethernet example**

| 222222        |

|---------------|

|               |

| 1x 81250A     |

| 1x 81250A-149 |

| 1x E4875A     |

| 1x 81250A-013 |

| 2x E4805B     |

| 6x E4832A     |

| 11x E4838A    |

| 6x E4835A     |

| 1x E4861A     |

| 1x E4862A     |

1x E4863A

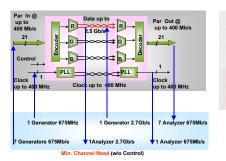

## Video (DVI), 1:7 MUX / DEMUX

Figure 13: Video (DVI) example

1x 81250A 1x 81250A-149 1x E4875A 1x 81250A-013 2x E4805B 4x E4832A 8x E4832A 4x E4835A 1x E4861A 1x E4862A 1x E4863A

### **Gigabit Ethernet**

Gigabit ethernet tranceivers take care for physical transreceiving data between a PC and a local network. The implementation consists of one chip, containing one TX and one RX. There is no clock at the serial side. (For 10 Gigabit Ethernet there would be signals running at 3.125 Gbit/s) For testing this device without the control inputs, 11x 675 Mbit/s Generator and Analyzer channels (1x Clock and 10x data) would be needed for the parallel side. On the serial side 1x 2.7 Gbit/s Generator and Analyzer are needed.

The 81250 configuration, shown in figure 14, contains all necessary resources to test Mux/Demux. As long as PRBS/PRWS data are used, both parts of the DUT can be tested at one run-time. If memory-based data is used, (due to synchronization limitations) only one part can be tested at one run time.

#### **Digital video**

For transferring data between CPU and Display, a digital video interface was created. The picture shown here is a simple example as there are several implementations created with more or less serial interconnections (up to 8). It is very common that the Mux/Demux ratio is 1:7 with all of these video interfaces. The DUT consists of two chips, one TX and one RX. Besides 3x serial there is also the clock at the speed of parallel side transferred.

For a minimum test of this device, the number of channels needed is counted to stimulate and analyze one of the three Mux/Demux paths. So this would need a total of 8x675 Mbit/s Generators and Analyzers (1x for clock, 7x for data) and 1x 2.7 Gbit/s Generator and Analyzer for the serial side.

The 81250 configuration, shown in figure 13, contains all necessary resource to test Mux/Demux. Testing is limited to one serial interface (either R, G or B). As long as PRBS/PRWS data are used both parts of DUT could be tested at one run-time. If memory-based data is used, (due to synchronization limitations) only one part can be tested at one run-time.

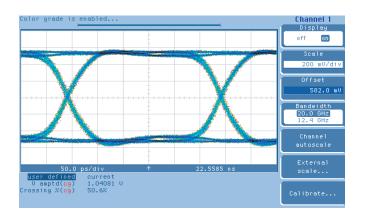

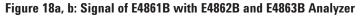

## **Signal Waveforms**

The following waveforms are taken from the different speed classes of the ParBERT family.

The pictures are taken showing once the Generator output on the scope and second the Analyzer Inputs are connected to an ideal source and with the help of the eye opening measurement (page 9) the performance of the Analyzer is recorded.

#### **ParBERT Settings:**

Generator and Analyzer in singleended mode, normal in/out used.

#### Frequency:

625 Mbit/s used for: E4808A + E4832A + E4838A + E4835A

2.5 Gbit/s used for: E4808A + E4861A + E4862A + E4863A

10.0 Gbit/s used for: E4808A + E4866A + E4867A

#### Data:

PRBS 2<sup>23</sup>-1 (stimulus and expected) data

**Generator levels**: Low Level -.4V, High levels + .4V

**Analyzer/Eye Opening:** Single-ended, terminated to ground Compared Bits 10<sup>6</sup> BER Threshold 10<sup>-3</sup>

**Trigger Out**: clock mode (625 MHz), levels O/1V

#### **Scope settings:**

Agilent 81600 DCA with 83484A 50 GHz module

- $\cdot$  connected with 1m SMA cables

- $\cdot$  external trigger from 81250

- trigger out

- $\cdot$  signal adjusted with Auto scale

- $\cdot$  every measurement for 300

- events

Ideal source: for 675 Mbit/s, 2.7 Gbit/s, 3.35 Gbit/s: transistion time 30ps, jitter <10ps pp, levels -.5V/OV

**For 10.8 Gbit/s:** transition time 10ps jitter <8ps pp, levels + - .4V

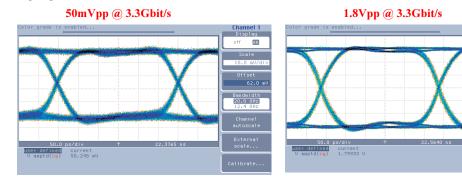

## **Eye plots**

The 3.35 Gbit/s Generator Output is designed for clean and fast output signals. It offers a swing of 50mV to 1.8V within voltage window suited for testing LVDS, CML, (P)ECL and SSTL -2 technologies.

Channel 1 Display off on

## **Crossing point**

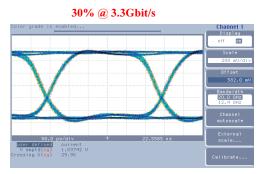

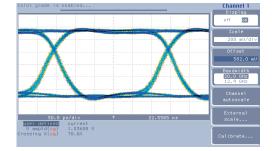

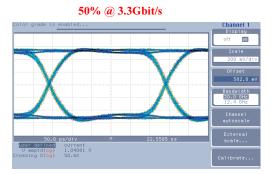

70% @ 3.3Gbit/s

The 3.35 Gbit/s Generator allows a variable cross-over for differential signals. The crossover can be programmed by the user interface or remote program between 30 to 70% .

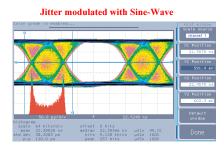

## Jitter modulation@3.3Gbit

Jitter modulated with Triangle-Wave

Jitter modulated with Rectangle-Wave

Jitter modulated with Noise-Generator

The 3.35 Gbit/s Generator has a Control Input for modulating the Delay with the help of an external signal. This modulation can be used to emulate jitter. The picture shows this modulatioin for different types of control voltages. The modulation can be used to test a DUT for jitter tolerance.

Figure 17a, b: Signals of E4832A with E4838A Generator and E4835A Analyzer

1.000e+ 30.0 m/v 40.0 m\v 0.0 ∨ -40.0 mV -80.0 mV -120.0 m<sup>1</sup> 0000. -160.0 m 200.0 m -240.0 m nnne. -280.0 m<sup>1</sup> -320.0 mV -360.0 mV -400.0 mV -440.0 mV -480.0 mV -520.0 mV -560.0 mV -600.0 mV -640.0 mV .000e-.000e-: .000e--680.0 m\ 30.0 ps 60.0 ps 90.0 ps 120.0 ps 150.0 ps 180.0 ps <scale> Relative -210.0 ps -150.0 ps -90.0 ps -30.0 ps -120.0 ps -120.0 ps -60.0 ps 0.0 s Show Copied Time Eye Voltage Eye Optimal Sample Opening Delay nal Sample Optima Voltage ort/Terminal 🖃 Meas (Abs. Volt (2) Data 462.409 m 275.152 m V

Figure 19a, b: Signal of E4866A Generator together with N4868A and E4867A Analyzer

## Agilent N4872A ParBERT 13.5 Gb/s Generator Agilent N4873A ParBERT 13.5 Gb/s Analyzer Technical Specifications

## Preliminary

## General

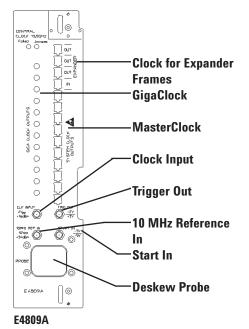

The N4872A Generator and N4873A Analyzer modules are each one VXI slot wide and operate in a range from 500 Mb/s up to 13.5 Gb/s. Some restrictions may apply at data rates between 500 Mb/s and 666 Mb/s. The ParBERT 13.5 Gb/s modules require the E4809A 13.5 GHz Central Clock module. All specifications, if not otherwise stated, are valid at the end of the recommended N4910A cable set (24" matched pair (2.4mm).

The N4872A Generator module generates hardware-based PRBS up to  $2^{31}$ -1, PRWS and user-defined patterns and provides a memory depth of 64 Mbit. The N4873A can synchronize on a 48bit detect word, or on a pure PRBS pattern without detect word.

#### **Timing Specifications**

The ParBERT 13.5 Gb/s modules are able to work with three different clock modes. The common clock mode is provided by the E4809A 13.5 GHz Central Clock module, which generates clock frequencies up to 13.5 GHz. The system also works synchronously with an external clock, which is connected to the E4809A clock module. Using the N4873A Analyzer module, CDR capabilities require the connecting of the Analyzer's CDR OUT to the E4809A clock module.

| Table 1: N4872A Data Generator Timing Specifications (@ 50 % of amplitude, 50 Ohm to GND) |                                                                |  |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Frequency range 500 MHz to 13.500 GHz                                                     |                                                                |  |

| Delay = Start delay+Fine delay                                                            | Can be specified as leading edge delay in fraction of bits in  |  |

|                                                                                           | each channel                                                   |  |

| Start Delay Range                                                                         | 0 to 100ns                                                     |  |

| Fine Delay Range                                                                          |                                                                |  |

| Data Rate: >666Mb/s                                                                       | ±1Period (can be changed without stopping)                     |  |

| Data Rate: <=666Mb/s                                                                      | 1,5ns (can be changed without stopping)                        |  |

| Delay Resolution                                                                          | 100 fs                                                         |  |

| Accuracy                                                                                  | $\pm 10$ ps $\pm 50$ ppm relative to the zero-delay placement. |  |

| Relative Delay Accuracy                                                                   | 1ps + 2%                                                       |  |

| Skew between modules of                                                                   | 20 ps after deskewing at customer levels and unchanged         |  |

| same type                                                                                 | system frequency.                                              |  |

Table 2: N4873A Analyzer Timing All timing parameters are measured at ECL levels, terminated with 50 Ohm to GND

Sampling rate

Same as generator

Sample Delay

Sample Delay = start delay + fine delay

Start Delay Range

Same as generator

Fine Delay Range

Same as generator

Resolution

Same as generator

Accuracy

Same as generator

Same as generator

Technical Specifications All specifications describe the instrument's warranted performance. Non-warranted values are described as typical. All specifications are valid from 10° to 40°C ambient temperature after a 30 minute warmup phase, with outputs and inputs terminate with 50 Ohms to ground at ECL levels if not specified otherwise.

#### Sequencing

The sequencer receives instructions from the central sequencer and generates a sequence according to that. The sequencer can also run without the central sequencer, generating its own sequence. Therefore it is possible to have ParBERT 13.5 Gb/s channels generating different sequences. The channel sequencer can generate a sequence with up to 120 segments. The sequencer has 2 loop levels, which allow nested loops.

An analyzer channel generates feedback signals that can control the channel sequencer and/or the central sequencer. In the case of parallel analyzer channels, the feedback has to be routed to the central sequencer to allow a common reaction of all parallel channels. In the case of a single receive channel, the channel sequencer itself can handle the feedback signals.

Skew

### **Pattern Generation**

The data stream is composed of segments. A segment can be made up of the memory-based pattern type, memory-based PRBS or hardware generated PRBS. A total of 64Mbit (at segment length resolution 512bits) are available for memorybased pattern and PRBS.

Memory-based PRBS is limited to 2<sup>15</sup>-1 or shorter. Memory-based PRBS allows special PRBS modes like zero substitution (also known as extended zero run) and variable mark ratio. A zero substitution pattern extends the longest zero series by a user selectable number of additional zeroes. The next bit following these zero series will be forced to 1. Mark ratio is the ratio of 1s and 0s in a PRBS stream, which is 1/2 in a normal PRBS. Variable mark ratio allows values of 1/8, 1/4, 1/2, 3/4 and 7/8.

Due to granularity reasons a PRBS has to be written to RAM several times, at a multiplexing factor of 512 the number of repetitions is also 512. That means that a 2<sup>15</sup>-1 PRBS uses up to 16Mbit of the memory. Hardware-based PRBS can be a polynomial up to a degree of  $2^{31}$ -1. No memory is used, so the total memory is free for memory-based pattern generation. Error insertion allows inserting single or multiple errors into a data stream. In case of an error a bit will be inverted, so instead of a 0 a 1 is put out and vice versa.

| Patterns:              |                                                                   |  |

|------------------------|-------------------------------------------------------------------|--|

| Memory based           |                                                                   |  |

| PRBS/PRWS              | Up to 64Mbit                                                      |  |

| Marker Density         | 2 <sup>n</sup> -1, n= 7, 9, 10, 11, 15                            |  |

| Errored PRBS/PRWS      | 1/8, 1/4, 1/2, 3/4, 7/8 at 2 <sup>n</sup> -1, n= 7, 9, 10, 11, 15 |  |

| Extended ones or zeros | 2 <sup>n</sup> -1, n= 7, 9, 10, 11, 15                            |  |

| Hardware based         |                                                                   |  |

| PRBS                   | 2 <sup>n</sup> -1, n= 7, 10, 11, 15, 23, 31                       |  |

| PRWS Port width        | 1, 2 , 4, 8, 16                                                   |  |

| Analyzer Auto-         | On PRBS or Memory-based Data                                      |  |

| synchronization        | Manual or automatic by:                                           |  |

|                        | Bit synchronization with or without                               |  |

|                        | automatic phase alignment                                         |  |

|                        | Automatic delay alignment around a start                          |  |

|                        | sample delay (Range: ±50ns)                                       |  |

|                        | BER Threshold: 10 <sup>-4</sup> to 10 <sup>-9</sup>               |  |

## N4872A Generator Module

The N4872A generates differential or single-ended data and clock signals operating from 500 Mb/s up to 13.5 Gb/s. The output levels are able to drive high-speed devices with interfaces like LVDS, ECL, PECL, CML and low voltage CMOS. The nominal output impedance is 50 Ohm typical. The Delay Control IN has a singleended input with 50 Ohm impedance. The input voltage allows one to modulate a delay element up to 1 GHz DC (200ps) within the Generator's differential output.

#### Data OUT

| Table 4: Parameters for N4872A Pare | BERT 13.5 Gb/s Generator                      |  |

|-------------------------------------|-----------------------------------------------|--|

| Data Output                         | 1, differential or single ended, 2.4mm(f) (1) |  |

| Impedance                           | 50 Ohm typ.                                   |  |